### Picosecond Time Stretcher and Time-to-Amplitude Converter Design and Simulations

Fukun Tang

Enrico Fermi Institute, The University of Chicago

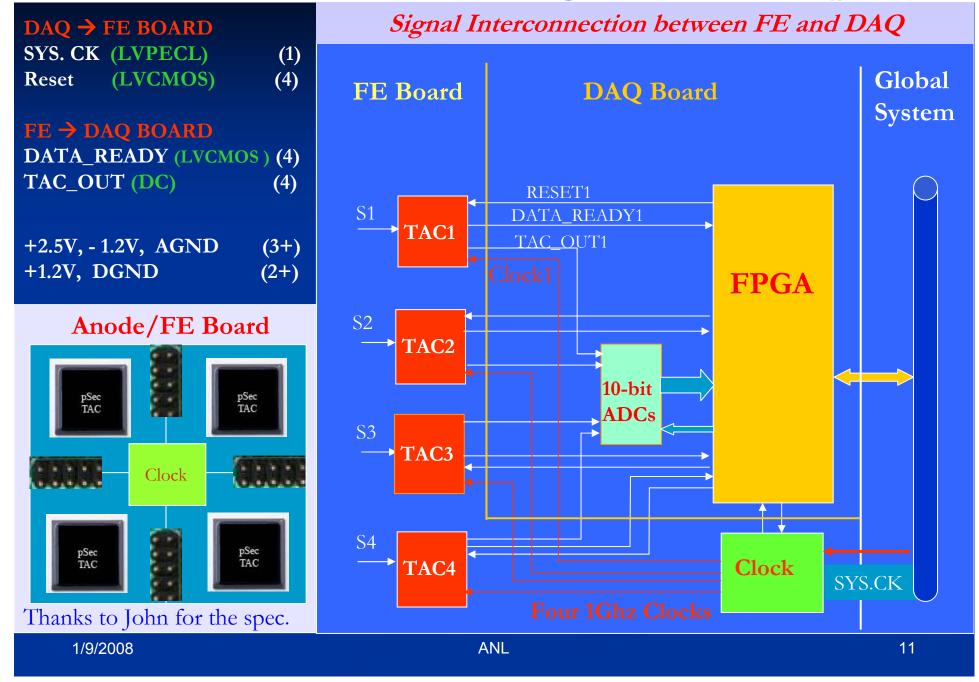

• Introduction

- Proposed Picosecond (pSec) Time Stretcher

- pSec Time Stretcher System Configuration

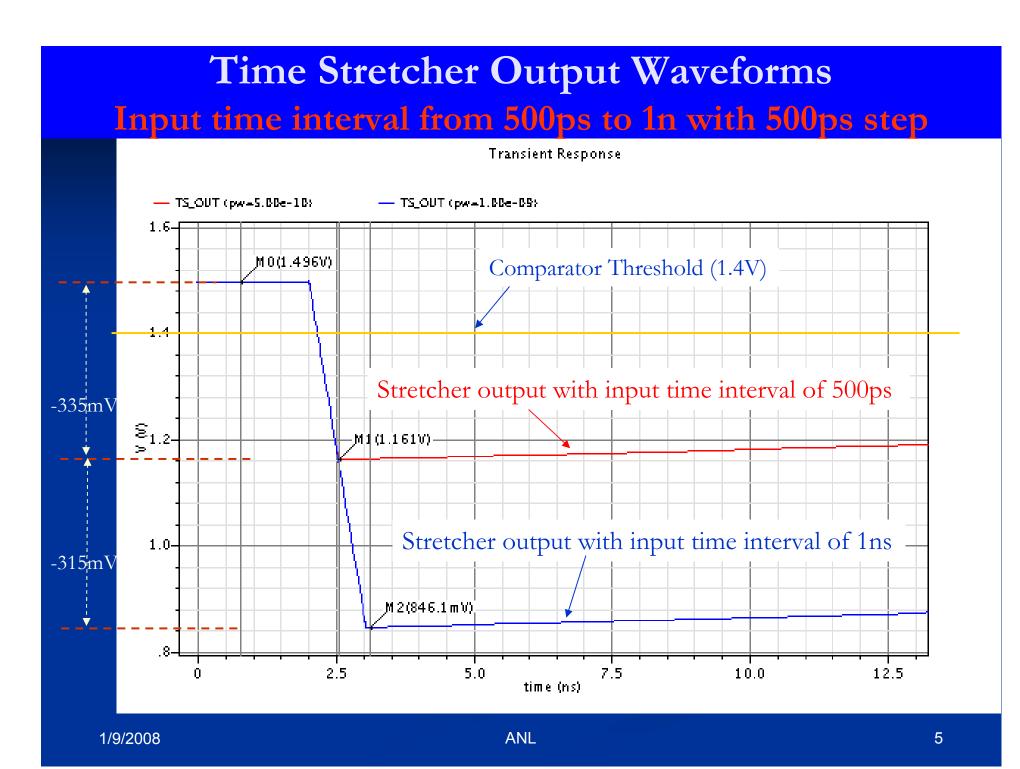

- pSec Stretcher Simulation Results

- The limitation of the pSec Time Stretcher

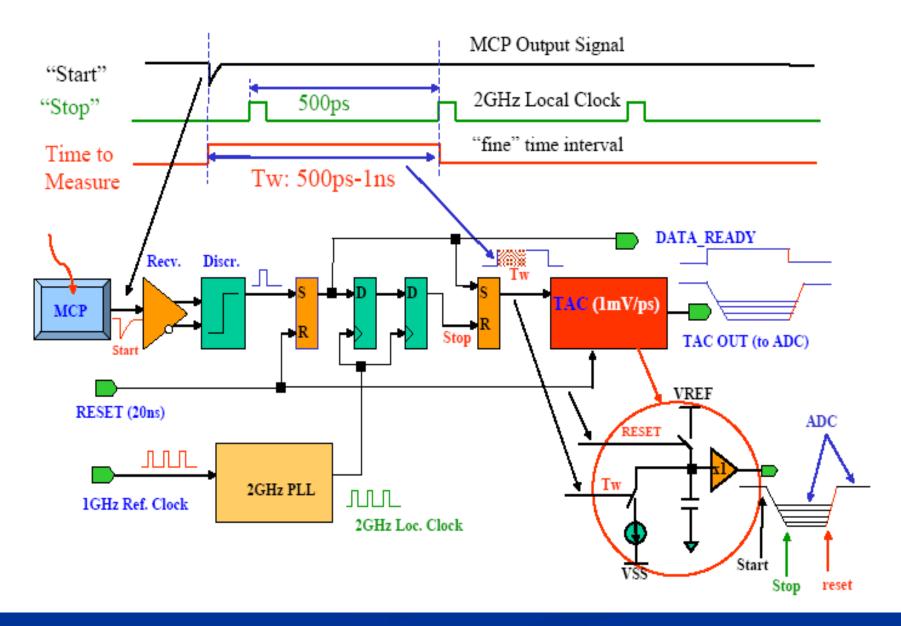

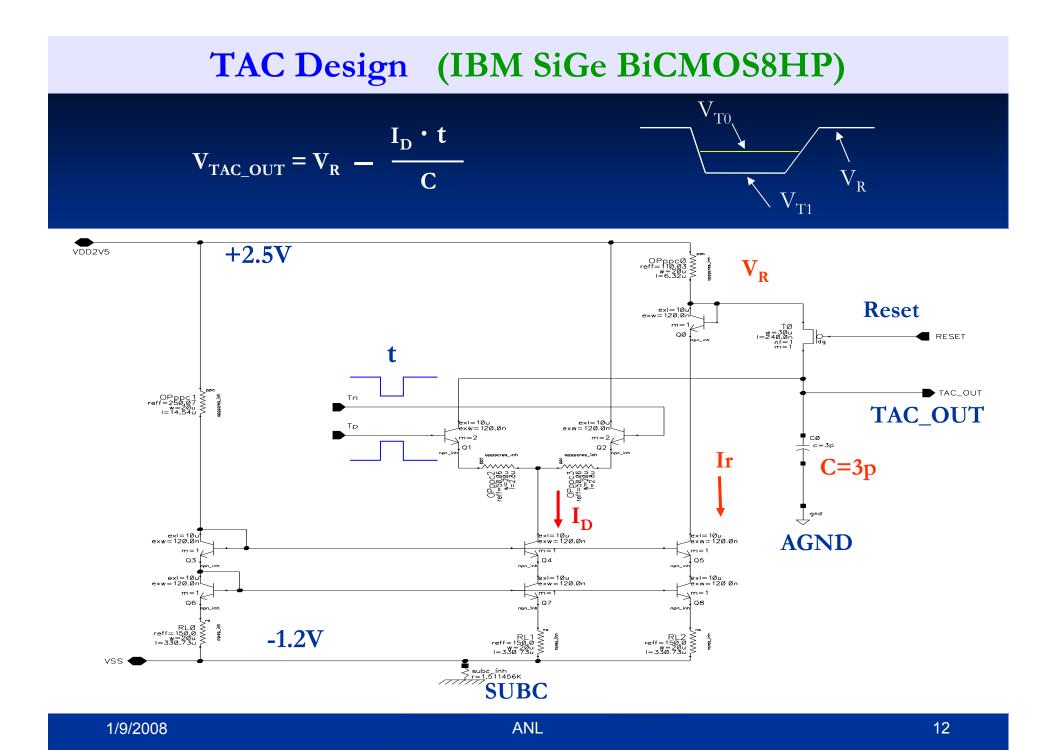

- Proposed pSec Time-to-Amplitude Converter (TAC)

- pSec TAC System Configuration

- pSec TAC Simulation Results

#### • Summary

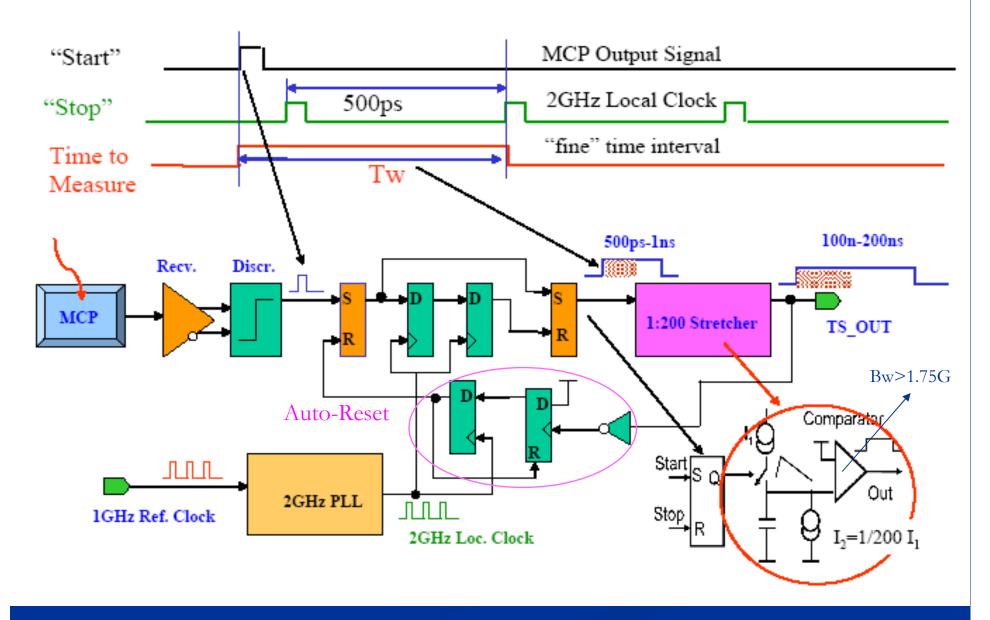

#### Proposed Time Stretcher Diagram

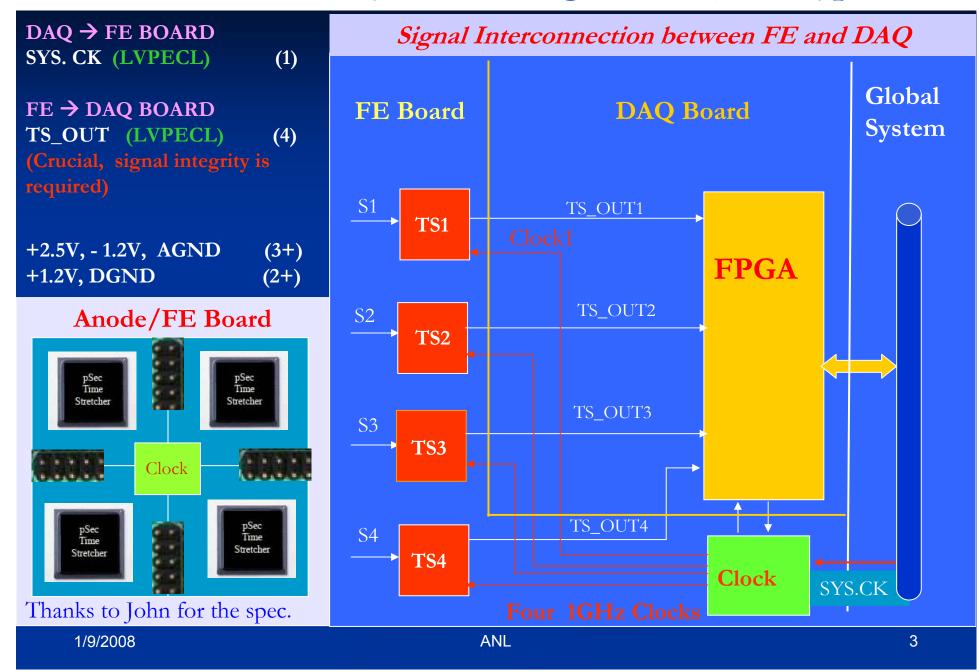

#### Time Stretcher System Configuration (Prototype)

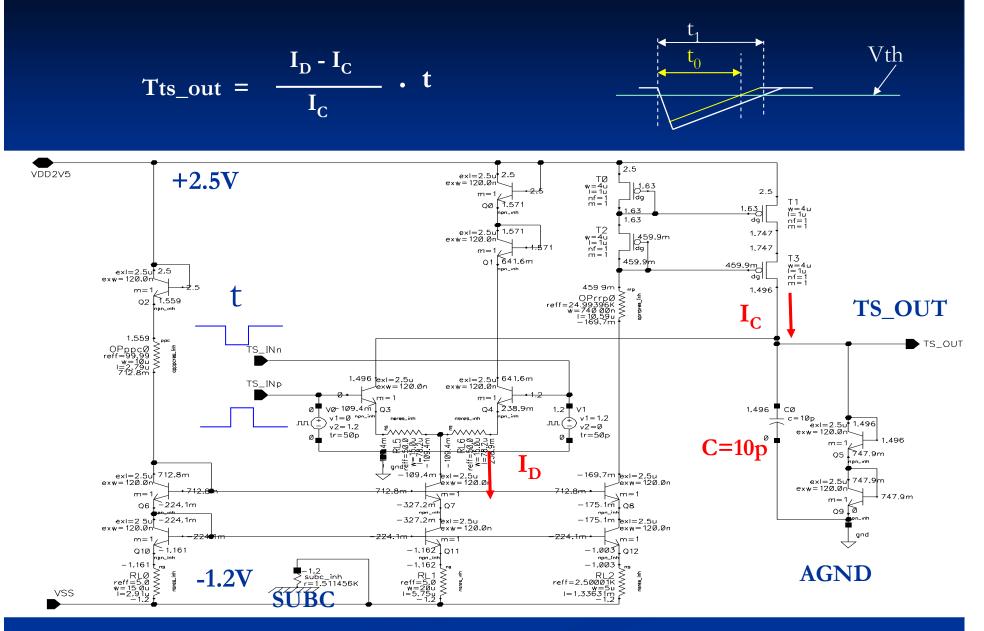

#### Time Stretcher Design (IBM SiGe BiCMOS8HP)

1/9/2008

ANL

### Slew Rate of the Time Stretcher Output

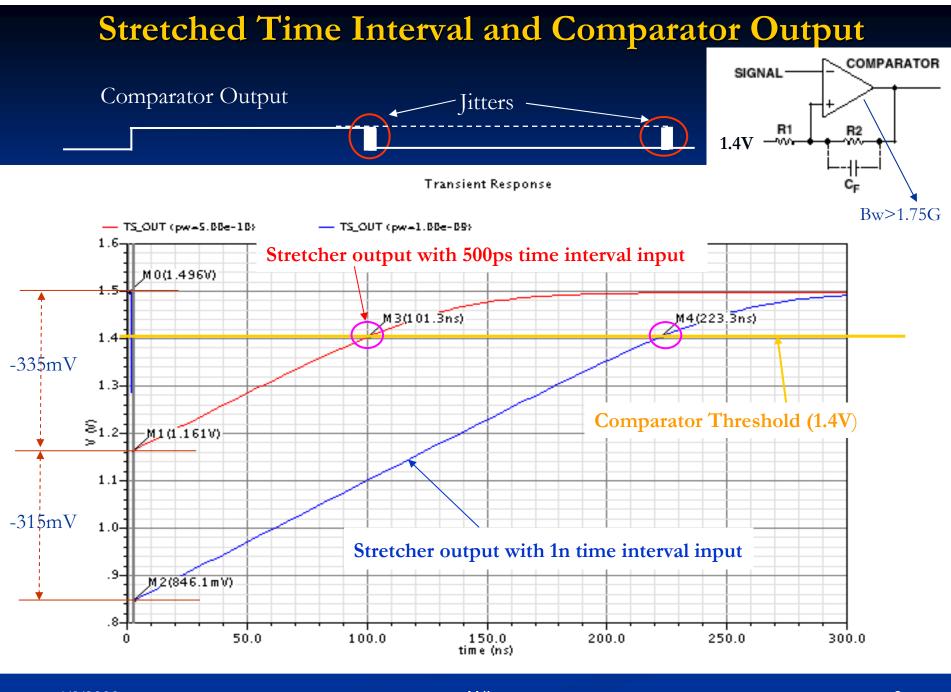

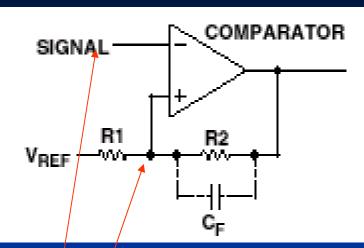

#### Design of Comparator with Hysteretic Threshold for Slow Slew Rate Input Signal

Slow Slew Rate Input Signal

Threshold

3 Major Factors With Comparator Design

(1) Timing Jitter ---- Noise & dv/dt

(2) Time Walk ---- Amplitude variations

(3) Drift ---- Rate & long term stability

Don't forget the crosstalk !

Comparator Jitter =

Vn dv/dt

Vn: Total noise from input signal and comparator over the bandwidth. dv/dt: Input signal slew rate (slope).

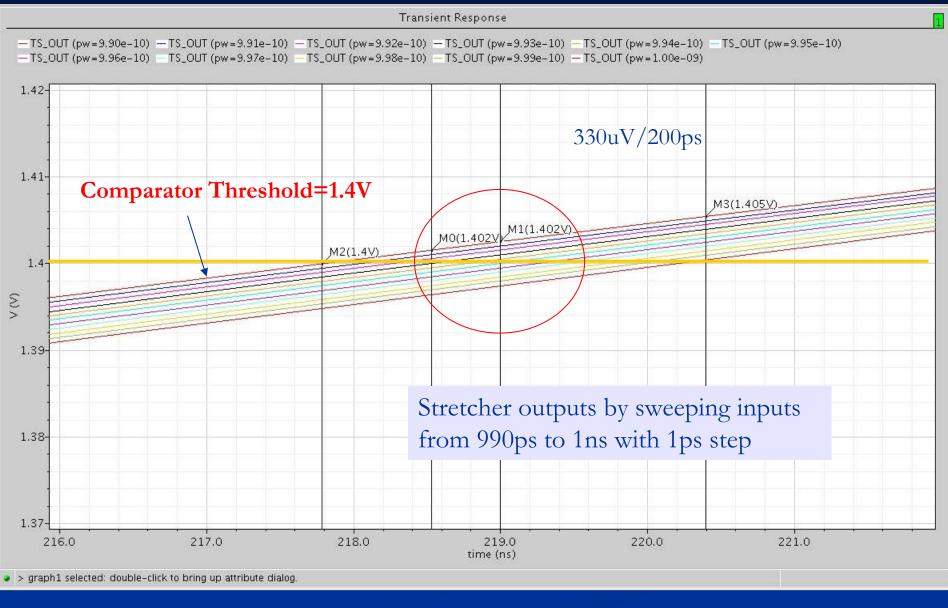

## The limitations of the Time Stretcher

- A minimum bandwidth of 1.75 Ghz comparator is required for the DAQ digitizer with 200ps LSB. (high speed, high power, high crosstalk).

- The slew rate (dv/dt) of the stretched analog signal is too small.

(330uV/200ps) comparing to the bandwidth of the comparator.

- The comparator threshold requires noise immunization and crosstalk rejection better than 330uV when input signal crosses the threshold.

- Frequent calibration may be required because threshold drift causing by the input signal rate and temperature variations.

- Lot of techniques are required to prevent the comparator from oscillating when the slow signal cross the threshold of an ultra-fast comparator (>1.75GHz).

- The estimated timing jitter missed our initial goal (1ps), based on the analysis of the electronics intrinsic noise, possible crosstalk and power supply noise both on stretched analog signal and the comparator threshold.

#### Proposed Time-to-Amplitude Converter (TAC)

#### Time Stretcher System Configuration (Prototype)

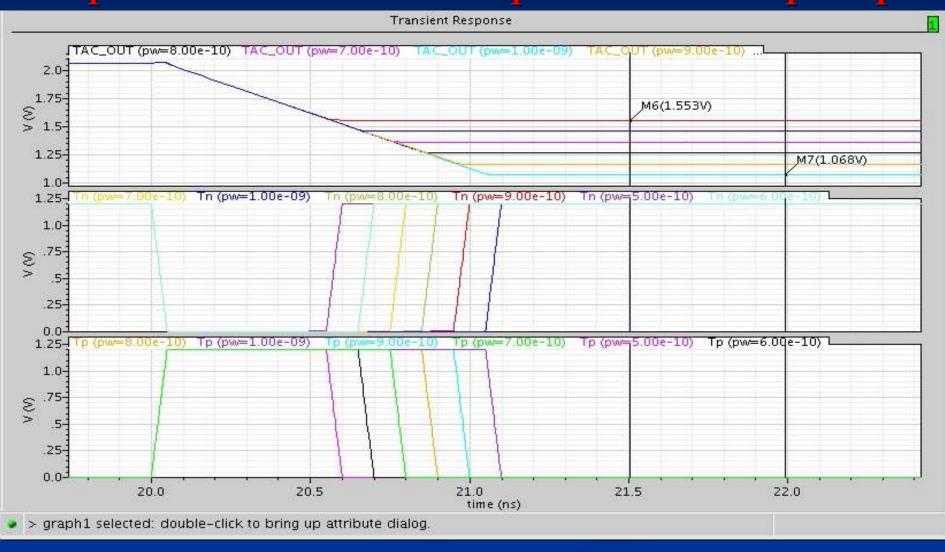

#### Input time intervals from 500ps-1ns with 100ps step

Transient Response TAC\_OUT (pw=8.0µe-10) TAC\_OUT (pw=7.00e-10) TAC\_OUT (pw=1.00e-10) TAC\_OUT (pw=9.00e-10) TAC\_OUT (pw=6.00e-10) 2.0-TAC OUT ≥<sup>1.75-</sup> ≥ 1.5-M0(1.553V) M1(1.456V) M2(1.359V)-M3(1.262V)--M4(1.165V) 1.25-M5(1.068V) 1.0-In (pw=1.00q-09) In (pw=8.00q-10) In (pw=9.00q-10) In (pw=5.00q-10) In (pw=6.00q 1.25-1 h (pw=//Ule-1 1.0-.75-NSN Diff\_Input (Tn) .5 .25-0.0-125- 1 (pw=8.002-10), (p(pw=1.002-09) (p(pw=9.002-10) (p(pw=7.002-10) (p(pw=5.002-10) (p(pw=5.002-10))) 1.0-.75-S > .5 Diff\_Input (Tp) .25-0.0 3.0- RESET (pw=9.00e-10) RESET (pw=1.00e-09) ipw=b UUe-1Ui RESET (pw=/.00e-10); W=5:01e-10) 2.5 ຣ<sup>2.0-</sup> ><sup>1.5-</sup> Reset 1.0 .5-0.0-20.0 30.0 50.0 60.0 70.0 80.0 40.0 time (ns) > graph1 selected: double-click to bring up attribute dialog. .ce12:Tp (pw=5.00e-10) ANL 1/9/2008

#### Input time intervals from 500ps to 1ns with 100ps step

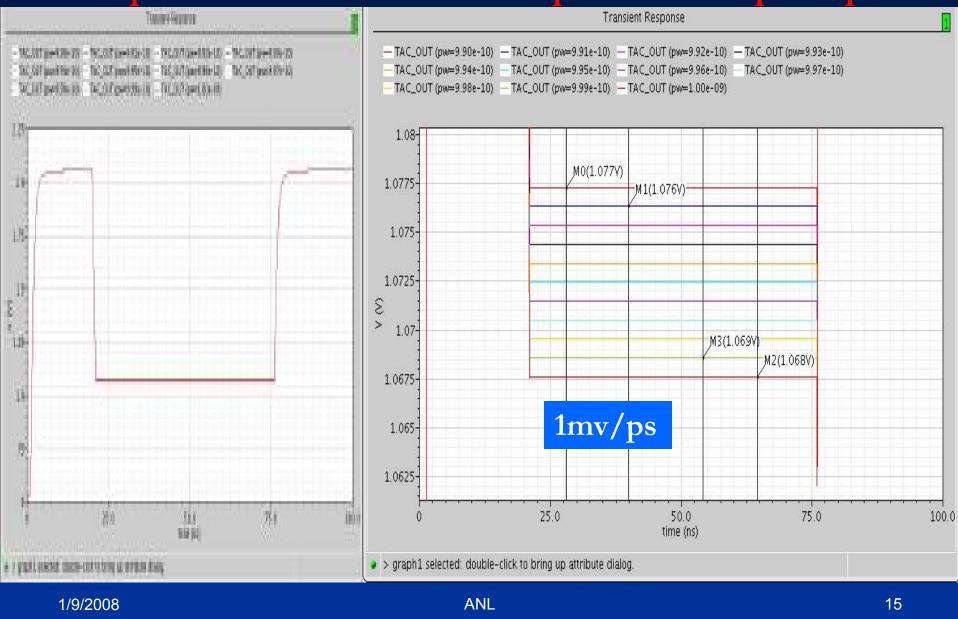

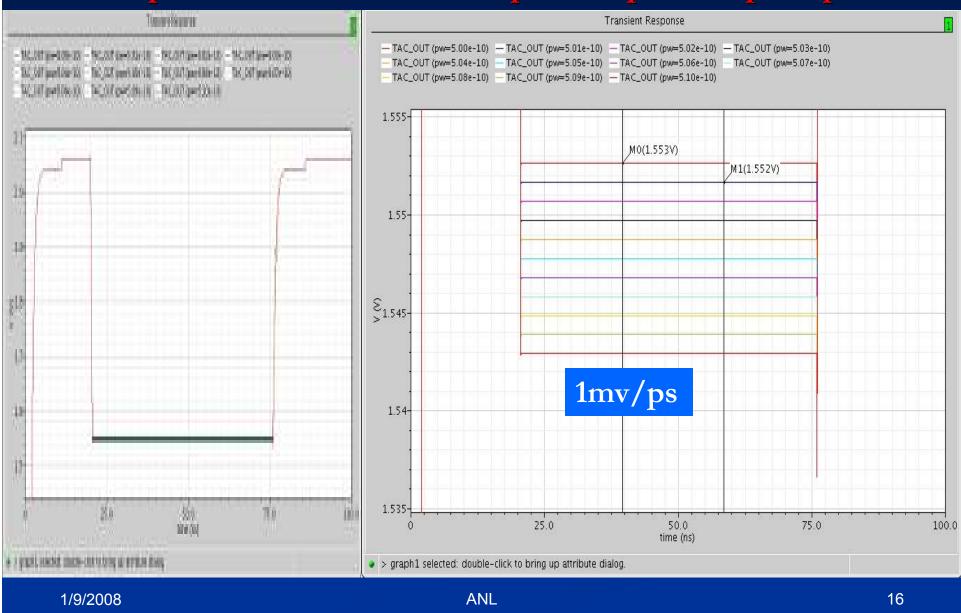

#### Input time intervals from 990ps-1ns with 1ps step

#### Input time intervals from 500ps to 510ps with 1ps step

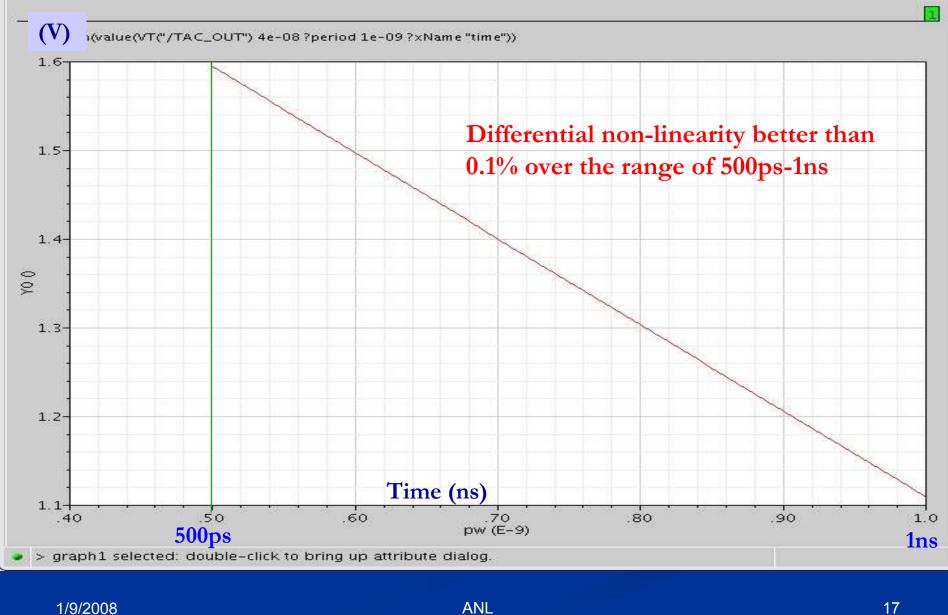

# **TAC Linearity**

#### Summary

Time Stretcher:

The main drawback is the limited dynamic range in ASIC design. The small signal slew rate (dv/dt) generates unacceptable jitters by the comparator. The estimated timing jitter out of the initial spec.

#### TAC:

- 1ps resolution is achievable (1mv/ps).

- Less techniques challenges on circuit design.

- Better linearity (One conversion instead of two).

- No fast signal transmission between FE to DAQ.

- Faster conversion (less system dead time).

With multiple sampling, the TAC output noise is reduced by a factor of Sqrt(N).

$\Delta \Sigma ADC$

S/H ADC with multiplexer **Sampling ADC**

----high rate, high bandwidth

- No special requirement for FPGA.

- Lower cost.

- 4-ch ADCs added.

- 8 more signals (4 DATA\_READY, 4 Reset) added.